## www.ramauniversity.ac.in

# FACULTY OF ENGINEERING AND TECHNOLOGY MEC-022 Lecture - 11

For all regions,

$$K_p = K'_p \frac{W}{L}$$

$K'_p = \mu_p C''_{\text{ox}}$   $i_G = 0$   $i_B = 0$  (4.29)

Cutoff region:

$$i_D = 0 \qquad \text{for } V_{GS} \ge V_{TP} \tag{4.30}$$

Triode region:

$$i_D = K_p \left( v_{GS} - V_{TP} - \frac{v_{DS}}{2} \right) v_{DS} \quad \text{for } 0 \le |v_{DS}| \le |v_{GS} - V_{TP}|$$

(4.31)

Saturation region:

$$i_D = \frac{K_P}{2} (v_{GS} - V_{TP})^2 (1 + \lambda |v_{DS}|) \quad \text{for } |v_{DS}| \ge |v_{GS} - V_{TP}| \ge 0 \quad (4.32)$$

Threshold voltage:

$$V_{TP} = V_{TO} - \gamma \left( \sqrt{v_{BS} + 2\phi_F} - \sqrt{2\phi_F} \right)$$

(4.33)

be

For the enhancement-mode PMOS transistor,  $V_{TP} < 0$ . For the depletion-mode PMOS,  $V_{TP} > 0$ .

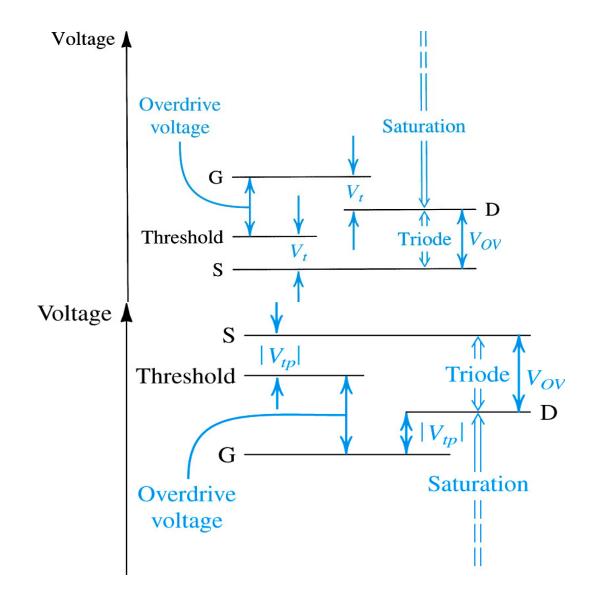

## NMOS and PMOS Summary (terminal voltages)

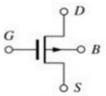

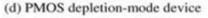

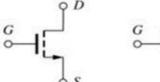

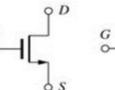

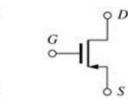

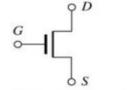

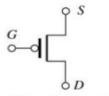

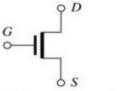

#### **MOSFET Circuit Symbols**

(a) NMOS enhancement-mode device

- (b) PMOS enhancement-mode device

- (c) NMOS depletion-mode device

(e) Three-terminal NMOS transistors

(f) Three-terminal PMOS transistors

(g) Shorthand notation—NMOS enhancement-mode device

(i) Shorthand notation—PMOS enhancement-mode device

<u>ò</u> S

(h) Shorthand notation—NMOS depletion-mode device

(j) Shorthand notation—PMOS depletion-mode device

- (g) and (i) are the most commonly used symbols in VLSI logic design.

- MOS devices are symmetric.

- In NMOS, n<sup>+</sup> region at higher voltage is the drain.

- In PMOS p<sup>+</sup> region at lower voltage is the drain

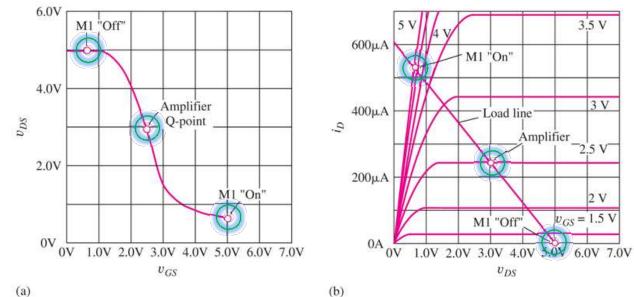

### **MOSFET** Analysis

Depending on the type of application, a MOSFET may be put into one of three ٠ regions of operation by setting its operating **Q-point**

(a)